半导体设备制造在当今科技领域占据着绝对核心的地位,是推动全球信息技术革命持续演进的关键力量。从智能手机的强大芯片到计算机的数据处理核心,从云计算的数据中心到人工智能的算法载体,无一不依赖于半导体设备制造所生产出的高精度、高性能设备来实现。它犹如一座灯塔,照亮了现代科技向着更小尺寸、更高性能、更低功耗方向发展的道路,并且在不断塑造和改变着我们的生活、工作以及整个社会的运行模式。

半导体制造工艺流程概述

半导体制造始于对高纯度半导体材料(如硅)的精心处理。首先是硅材料的提纯,通过化学气相沉积(CVD)等方法去除杂质,得到纯度高达 99.9999% 以上的单晶硅。随后利用提拉法或区熔法将单晶硅生长成单晶硅棒,再经过切割、研磨和抛光等工序,制备出具有极高平整度和光洁度的晶圆,其厚度通常在几百微米左右,为后续的芯片制造提供基础材料。

芯片制造的核心工艺流程包括光刻、刻蚀、薄膜沉积、离子注入、扩散等多个步骤,且这些步骤需要在高度洁净的环境中反复进行。光刻工艺利用光刻机将设计好的电路图案精确地投影到晶圆表面的光刻胶上,通过曝光、显影等操作将图案转移到晶圆;刻蚀工艺则根据光刻图案,有选择性地去除晶圆表面的材料,以形成精细的电路结构;薄膜沉积工艺在晶圆表面沉积各种功能薄膜,如二氧化硅绝缘膜、金属导电膜等,为芯片构建不同的电学和物理特性;离子注入工艺通过将特定的杂质离子注入到晶圆的特定区域,精确地改变半导体材料的电学性质,如形成 pn 结等关键结构;扩散工艺则是在高温条件下,使杂质原子在半导体材料中扩散,以调整材料的电学参数。

在完成芯片制造的前端工艺后,还需要进行芯片的封装和测试。封装工艺将芯片与外部引脚或基板进行连接,并使用塑料、陶瓷等材料对芯片进行保护,以提高芯片的机械强度、散热性能和电气性能,同时便于芯片在电路板上的安装和使用。测试工艺则对封装前后的芯片进行全面的电学性能测试,包括功能测试、参数测试等,以筛选出合格的芯片,确保其质量和可靠性。

半导体设备的主要类型与功能

光刻设备:光刻设备是半导体制造中最为关键的设备之一,其精度直接决定了芯片的制程工艺水平。光刻机主要由光源、光学投影系统、晶圆工作台和控制系统等部分组成。光源发出的紫外光或极紫外光(EUV)经过复杂的光学系统进行准直、滤波和聚焦后,投射到涂有光刻胶的晶圆上。晶圆工作台能够实现高精度的 X、Y、Z 轴移动和旋转,确保晶圆在曝光过程中的精确位置。控制系统则负责协调光源、光学系统和工作台之间的动作,根据芯片设计的图案数据,精确控制曝光的时间、强度和位置等参数。例如,在先进的 7 纳米及以下制程的芯片制造中,极紫外光刻机能够实现更小的特征尺寸光刻,其光源波长可低至 13.5 纳米,能够在晶圆上刻画出极其精细的电路图案,为高性能芯片的制造提供了可能。

刻蚀设备:刻蚀设备分为干法刻蚀和湿法刻蚀两种类型,其中干法刻蚀在现代半导体制造中应用更为广泛。干法刻蚀设备主要利用等离子体刻蚀技术,通过在反应腔室内产生等离子体,使等离子体中的活性离子与晶圆表面的材料发生化学反应或物理轰击,从而去除不需要的材料。刻蚀设备的关键部件包括射频电源、反应腔室、气体供应系统和晶圆夹具等。射频电源为反应腔室内的气体提供能量,使其电离形成等离子体;反应腔室提供了刻蚀反应的空间环境,其内部的温度、压力和气流等参数需要精确控制;气体供应系统则根据不同的刻蚀工艺要求,精确地向反应腔室输送各种刻蚀气体,如氟气、氯气等;晶圆夹具负责固定晶圆,并确保其在刻蚀过程中的均匀性和稳定性。例如,在制造多层金属互连结构的芯片时,刻蚀设备需要精确地刻蚀出金属线条和通孔,其刻蚀精度可达到纳米级别,以保证不同金属层之间的良好电气连接。

薄膜沉积设备:薄膜沉积设备用于在晶圆表面沉积各种功能薄膜,包括化学气相沉积(CVD)设备和物理气相沉积(PVD)设备。CVD 设备是通过化学反应在晶圆表面生成薄膜,其原理是将气态的前驱体物质在高温或等离子体的作用下分解并在晶圆表面发生化学反应,形成固态的薄膜。CVD 设备的主要组成部分包括反应腔室、气体供应系统、加热系统和真空泵等。反应腔室是薄膜沉积的核心区域,其内部的温度、压力和气体流量等参数对薄膜的质量有着至关重要的影响;气体供应系统负责提供各种反应气体,如硅烷、氨气等;加热系统用于升高反应腔室的温度,以促进化学反应的进行;真空泵则用于维持反应腔室的真空环境,排除反应副产物。PVD 设备则是利用物理过程,如蒸发或溅射,将固态的靶材原子沉积到晶圆表面形成薄膜。PVD 设备通常包括真空腔室、靶材、离子源和晶圆支架等部件。例如,在制造集成电路的绝缘层时,常采用化学气相沉积的方法生长二氧化硅薄膜;而在制备金属薄膜,如铝或铜薄膜时,则多使用物理气相沉积设备。

离子注入设备:离子注入设备能够将特定的杂质离子(如硼离子、磷离子等)以精确的能量和剂量注入到晶圆的特定区域,从而改变半导体材料的电学性质,实现对芯片性能的精准调控。离子注入设备主要由离子源、加速管、质量分析器、扫描系统和晶圆处理室等部分组成。离子源产生所需的杂质离子,加速管将离子加速到预定的能量,质量分析器用于筛选出特定质量的离子,以确保注入离子的纯度和准确性;扫描系统则控制离子束在晶圆表面的扫描方式和范围,实现均匀的离子注入;晶圆处理室提供了晶圆在注入过程中的环境,并配备有冷却系统,以防止注入过程中晶圆温度过高。例如,在制造 pn 结时,通过精确控制硼离子和磷离子的注入剂量和能量,可以调整 pn 结的深度和浓度,从而影响芯片的电学特性,如正向导通电压、反向击穿电压等。

封装设备:封装设备负责将制造好的芯片进行封装,以保护芯片免受外界环境的影响,并实现芯片与外部电路的电气连接和物理机械固定。封装设备包括引线键合设备、倒装芯片键合设备、塑封设备等。引线键合设备是传统封装工艺中常用的设备,它通过使用细金属丝(如金线)将芯片上的电极与封装基板上的引脚连接起来,其关键技术在于精确控制金属丝的直径、长度和键合位置,以确保良好的电气连接和机械稳定性。倒装芯片键合设备则是将芯片的电极直接与封装基板上的对应焊盘进行面对面的焊接,这种方式可以提高芯片与基板之间的电气性能和散热性能,但对芯片和基板的平整度以及焊接工艺要求更高。塑封设备用于将封装好的芯片用塑料材料进行封装,以提供机械保护、防潮、散热等功能,其主要工作原理是将液态的塑料材料注入到模具中,在高温高压下使其固化成型,包裹住芯片和连接线路。例如,在手机芯片的封装中,采用先进的倒装芯片键合和塑封技术,可以减小封装体积,提高芯片的散热性能和可靠性,从而满足手机小型化、高性能的需求。

测试设备:测试设备贯穿于半导体制造的整个过程,包括晶圆测试设备和成品芯片测试设备。晶圆测试设备在晶圆制造完成后,对晶圆上的每个芯片进行初步的电学性能测试,主要测试项目包括芯片的开路、短路、阈值电压、漏电电流等参数,通过探针卡与晶圆上的芯片电极进行接触,将测试信号输入到芯片中,并采集芯片的输出信号,以判断芯片是否存在制造缺陷。成品芯片测试设备则在芯片封装完成后,对成品芯片进行全面的功能和性能测试,其测试内容更为复杂,包括芯片的逻辑功能测试、运算速度测试、功耗测试、可靠性测试等。成品芯片测试设备通常采用自动化测试系统,通过测试夹具将芯片与测试设备连接起来,根据不同的芯片类型和测试要求,运行相应的测试程序,对芯片进行全方位的检测。例如,在高性能计算机芯片的测试中,需要对芯片的复杂逻辑功能和高速运算能力进行严格测试,以确保其在实际应用中的可靠性和稳定性。

光刻技术的核心要点与发展趋势

光刻技术的核心在于实现高精度的图案转移。在传统的光刻工艺中,光源的波长是影响光刻精度的关键因素之一。随着芯片制程工艺的不断缩小,从早期的紫外光(UV)光刻逐渐发展到深紫外光(DUV)光刻,再到如今的极紫外光(EUV)光刻。例如,DUV 光刻技术采用的波长为 193 纳米或 248 纳米,能够满足 65 纳米至 14 纳米制程芯片的制造需求;而 EUV 光刻技术的波长为 13.5 纳米,为 7 纳米及以下制程芯片的制造提供了关键技术支持。

除了光源波长的不断缩短,光刻技术还依赖于高精度的光学投影系统。光学投影系统需要具备高数值孔径(NA),以提高成像的分辨率。同时,为了补偿由于光源波长缩短和数值孔径增大带来的光学像差问题,光刻技术采用了复杂的光学补偿技术,如离轴照明、相移掩膜等。离轴照明通过改变光源的照射角度,提高了光刻图案的对比度;相移掩膜则利用相位差原理,使相邻的光刻图案之间产生相位变化,从而提高了光刻的分辨率。

光刻胶也是光刻技术中的重要组成部分。光刻胶的性能直接影响到光刻图案的质量和分辨率。随着光刻工艺的发展,对光刻胶的要求也越来越高,如需要具备更高的感光度、分辨率、对比度和抗刻蚀性等。例如,在 EUV 光刻工艺中,需要开发新型的 EUV 光刻胶,其化学结构和性能与传统光刻胶有很大的不同,能够更好地适应 EUV 光的曝光特性和高分辨率要求。

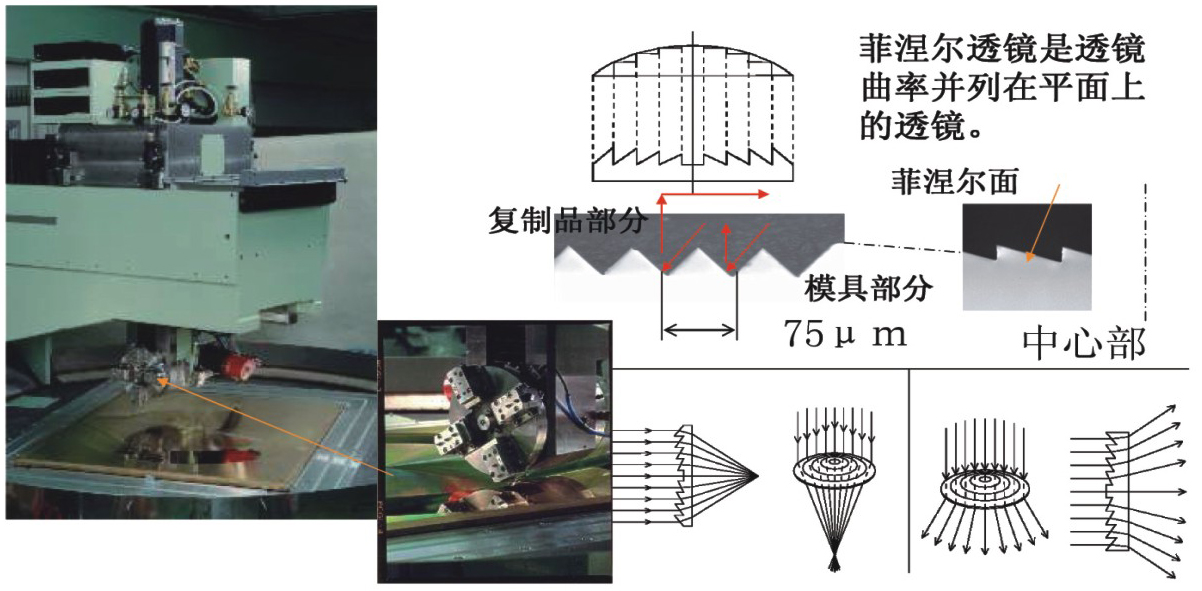

光刻技术的发展趋势是不断追求更高的分辨率和更小的特征尺寸。未来,除了继续改进 EUV 光刻技术,如提高 EUV 光源的功率和稳定性、优化光学投影系统等,还可能会探索新的光刻技术,如纳米压印光刻、电子束光刻等。纳米压印光刻利用模具将图案压印到光刻胶上,具有较高的分辨率和较低的成本,但在大规模生产中的应用还面临一些技术挑战;电子束光刻则具有极高的分辨率,可用于制造高精度的掩膜版或特殊的纳米级芯片结构,但由于其生产效率较低,目前主要应用于科研和小批量生产领域。

刻蚀工艺的技术要点与挑战

刻蚀工艺的关键技术在于实现高精度、高选择性和各向异性的刻蚀。在等离子体刻蚀过程中,需要精确控制等离子体的参数,如等离子体的密度、能量、温度等,以确保刻蚀反应的准确性和稳定性。例如,通过调整射频电源的功率、频率和气体流量等参数,可以控制等离子体的密度和能量,从而实现对不同材料的刻蚀速率和刻蚀选择性的控制。

刻蚀工艺面临的主要挑战之一是如何在提高刻蚀速率的同时,保证刻蚀的精度和选择性。随着芯片制程的不断缩小,对刻蚀的精度要求越来越高,如在制造纳米级的芯片结构时,刻蚀的线宽偏差需要控制在极小的范围内。同时,为了避免对其他不需要刻蚀的材料造成损伤,需要提高刻蚀的选择性,即在刻蚀目标材料时,尽量减少对相邻材料的刻蚀。例如,在制造多层金属互连结构时,需要精确地刻蚀出金属线条和通孔,同时要保护下层的绝缘层和其他金属层,这就要求刻蚀工艺具有极高的选择性和精度。

另一个挑战是如何实现深宽比(刻蚀深度与宽度之比)较大的刻蚀结构。在一些芯片制造工艺中,如动态随机存取存储器(DRAM)的制造,需要制造深宽比较大的沟槽或通孔,这对刻蚀工艺的稳定性和均匀性提出了很高的要求。为了实现深宽比大的刻蚀结构,需要采用特殊的刻蚀技术,如 Bosch 刻蚀工艺,该工艺通过交替进行刻蚀和沉积步骤,在刻蚀侧壁上形成保护膜,防止侧壁的过度刻蚀,从而实现深宽比大的刻蚀结构。

薄膜沉积工艺的技术细节与创新方向

薄膜沉积工艺的技术细节包括对薄膜厚度、均匀性、化学成分和晶体结构等参数的精确控制。在化学气相沉积(CVD)工艺中,反应气体的种类、流量、温度、压力等参数对薄膜的质量有着重要的影响。例如,在制备二氧化硅薄膜时,通过调整硅烷和氧气的流量比、反应温度和压力等参数,可以控制二氧化硅薄膜的厚度、折射率和致密性等特性。

在物理气相沉积(PVD)工艺中,靶材的选择、溅射功率、气体压力等参数决定了薄膜的沉积速率、均匀性和化学成分。例如,在制备金属薄膜时,选择不同的金属靶材(如铝、铜、钛等),并调整溅射功率和气体压力,可以得到不同厚度、纯度和晶体结构的金属薄膜。

薄膜沉积工艺的创新方向主要集中在提高薄膜的质量和性能,同时降低工艺成本和环境影响。例如,开发新型的 CVD 工艺,如原子层沉积(ALD)工艺,该工艺能够实现原子级别的薄膜厚度控制,具有极高的薄膜均匀性和台阶覆盖率,在制造高 k 绝缘材料、金属栅极等关键芯片结构时具有重要应用价值。此外,还在研究如何采用绿色环保的薄膜沉积工艺,减少对有毒有害气体的使用,以满足日益严格的环保要求。

离子注入工艺的技术关键与优化策略

离子注入工艺的技术关键在于精确控制注入离子的种类、能量、剂量和注入深度。离子源的性能直接影响到注入离子的纯度和稳定性。例如,采用先进的离子源技术,如射频离子源或电子回旋共振(ECR)离子源,可以产生高纯度、高能量稳定性的离子束,满足不同芯片制造工艺的需求。

加速管的设计和性能决定了离子的加速效果,需要确保离子能够达到预定的能量。质量分析器则用于筛选出特定质量的离子,保证注入离子的准确性。例如,在制造半导体器件时,需要精确地注入硼离子或磷离子,质量分析器能够有效地去除其他杂质离子,提高注入离子的纯度。

扫描系统的精度和均匀性对晶圆上离子注入的均匀性起着关键作用。通过优化扫描系统的设计,如采用高精度的电机驱动和扫描算法,可以实现离子束在晶圆表面的均匀扫描,确保整个晶圆上的离子注入剂量均匀一致。

离子注入工艺的优化策略包括提高注入效率、降低晶圆损伤和减少工艺成本。例如,采用低温离子注入技术,可以减少注入过程中晶圆的温度升高,从而降低对晶圆的热损伤;开发新型的离子注入设备,提高设备的自动化程度和生产效率,降低设备的购置和运行成本。

半导体基础材料的特性与制备

硅是最常用的半导体基础材料,其具有良好的半导体特性,如可控的电学性质、较高的晶体稳定性和丰富的资源储量。单晶硅的制备通常采用提拉法或区熔法。提拉法是将籽晶浸入到盛有熔硅的坩埚中,通过缓慢提拉籽晶,并同时旋转籽晶和坩埚,使熔硅在籽晶上逐渐凝固生长成单晶硅棒。区熔法是利用高频感应线圈使硅棒局部熔化,通过移动硅棒或感应线圈,使熔化区域从一端移动到另一端,从而实现硅的提纯和单晶硅的生长。

除了硅,还有一些其他的半导体材料也在特定的应用领域中得到应用,如砷化镓(GaAs)具有较高的电子迁移率和光电性能,适用于制造高速电子器件和光电器件。砷化镓的制备方法包括水平 Bridgman 法、液封 Czochralski 法等。水平 Bridgman 法是将装有砷化镓原料的坩埚置于温度梯度炉中,通过缓慢移动坩埚,使原料在坩埚底部逐渐凝固生长成砷化镓晶体;液封 Czochralski 法是在提拉法的基础上,采用一种不与砷化镓反应的液体(如硼酸)覆盖在熔砷化镓表面,以防止砷的挥发,然后提拉籽晶生长砷化镓晶体。

先进材料在半导体设备制造中的应用与研究进展

随着半导体技术的不断发展,一些先进材料开始在半导体设备制造中得到应用。例如,高 k 绝缘材料(如 hafnium oxide)在集成电路制造中用于取代传统的二氧化硅作为栅极绝缘层,以解决随着芯片制程缩小而出现的漏电问题。高 k 绝缘材料的研究重点在于提高其与硅衬底的界面质量、降低缺陷密度和优化其电学性能。

金属栅极材料(如 titanium nitride、钽 nitride 等)也逐渐取代传统的多晶硅栅极,以提高芯片的性能。金属栅极材料的研究方向包括提高其功函数的调控能力、增强其与高 k